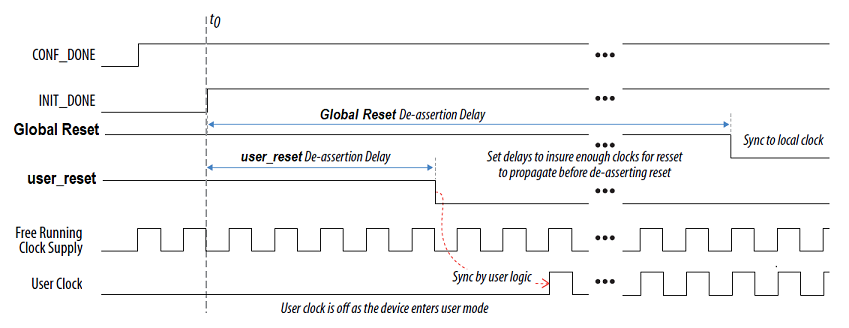

Sau khi thiết Intel® Stratix® 10 hoàn tất cấu hình và vào chế độ người dùng, bạn được yêu cầu triển khai trình tự đặt lại trước khi chạy ứng dụng của mình. Khi hoàn thành giai đoạn cấu hình, các chức năng của thiết bị Intel Stratix 10 dự kiến sẽ không đi vào chế độ người dùng đồng thời. Khi thiết bị vào chế độ người dùng, một đồng hồ chạy miễn phí có thể gây ra điều kiện chạy đồng hồ giữa logic người dùng làm hỏng các điều kiện ban đầu của thiết bị.

Để ngăn chặn sự kiện này, Intel khuyến nghị bạn nên xây dựng thiết kế bằng IP Intel Stratix Clock Gate Intel Stratix 10 FPGA với logic người dùng của riêng bạn để hủy cổng Đồng hồ Người dùng và hủy hiển thị tín hiệu Đặt lại toàn cầu như trong Hình 1. Sử dụng lõi IP FPGA Intel Stratix Đặt lại người dùng và Xung Intel Stratix để hủy hiển thị tín hiệu từ cổng user_reset để hủy cổng Đồng hồ Người dùng. Sau đó, xây dựng logic của riêng bạn để hủy hiển thị tín hiệu Global Reset sau khi bạn đã bỏ cổng Đồng hồ Người dùng.

Lưu ý rằng Đồng hồ Chạy Miễn phí là một đồng hồ có nguồn gốc bên ngoài, làm thay đổi Đồng hồ Người dùng là một đồng hồ mà đồng hồ mà người dùng đồng hồ trong môi trường FPGA. Đồng hồ Người dùng cũng có thể là một đồng hồ chạy miễn phí hoặc một vòng lặp khóa pha (PLL) được tạo ra đồng hồ.

Dự kiến, chỉ cần sử dụng một phiên bản IP duy nhất để điều chỉnh tất cả đồng hồ của người dùng, sử dụng tín hiệu đặt lại toàn cầu để phát hành/loại bỏ đòi hỏi đặt lại trong nhiều tên miền. Nếu thiết kế có nhiều tên miền đặt lại, hãy đảm bảo tín hiệu đặt lại toàn cầu được tổ chức đủ lâu để tín hiệu truyền đến tất cả các tên miền trước khi hủy kết quả.

Hình 1. Thiết lập lại người dùng và Sơ đồ khối gating đồng hồ

Lưu ý: Không sử dụng cổng user_clkgate cổng User Reset and Clock Gate Intel Stratix IP FPGA 10.

Độ trễ de-assertion đề xuất cho tín hiệu user_reset bằng cách sử dụng IP Cổng xung và Đặt lại người dùng FPGA Intel Stratix 10 và độ trễ hủy hủy xác nhận cho tín hiệu Đặt lại toàn cầu

Độ trễ user_reset hủy xác nhận tín hiệu phải nhiều hơn một chu kỳ Đồng hồ người dùng. Bạn có thể nhận được độ trễ mong muốn bằng cách nhập giá trị Độ trễ hủy hủy xác nhận trong IP Intel Stratix xung Intel Stratix IP FPGA người dùng. Các giá trị có thể cho tham số De-assertion Delay trong IP Intel Stratix Clock Gate Intel Stratix 10 FPGA có thể dao động từ 0 ns đến 65,535 ns. Bạn phải xây dựng một trình đồng bộ bằng cách sử dụng kỹ thuật chống metastable tiêu chuẩn bên trong:

- Logic người dùng để Ungate User Clock để đồng bộ hóa tín user_reset của bạn đối với đồng hồ chạy miễn phí.

- Logic người dùng để hủy hiển thị Global Reset để đồng bộ hóa tín user_reset của người dùng đối với Đồng hồ người dùng.

Độ trễ de-assertion tín hiệu Global Reset phải đủ lâu để tín hiệu Global Reset truyền tới logic đặt lại toàn cầu trong hệ thống của bạn sau khi User Clock đang chạy. Xây dựng logic người dùng của riêng bạn để hủy hiển thị tín hiệu Global Reset sau khi user_reset được hủy hiển thị và User Clock đang chạy. Bạn cũng phải đồng bộ hóa tín hiệu Global Reset đối với Đồng hồ người dùng bằng cách sử dụng các kỹ thuật chống metastable tiêu chuẩn.

Hình 2. Thiết lập lại người dùng và Sơ đồ thời gian gating đồng hồ

Thông tin này được ghi lại trong Hướng dẫn Sử dụng Cấu hình Intel Stratix 10 mới nhất cho Phần mềm Intel® Quartus® Prime Phiên bản Pro v19.1.