Do không có các hạn chế JTAG phù hợp, bạn có thể thấy lỗi "Cài đặt không thu nạp kênh TX/RX/LINK|* " trong Bộ thu phát Intel® Toolkit khi tải thiết kế có kênh trên nhiều ô. Do vị trí logic mềm PHY gốc, các vấn đề thường được quan sát thấy nhất khi bạn có nhiều khởi tạo PHY riêng trên các ô khác nhau.

Giải pháp là hạn chế đồng hồ định cấu hình lại được đưa vào cổng định cấu hình lại của PHY riêng. Xác nhận rằng 'altera_reserved_tck' và đồng hồ được kết nối với cổng đồng hồ định cấu hình lại 'rcfg_clk' của PHY gốc đã bị hạn chế và chuyển thời gian chính xác trong TimeQuest. Đồng hồ này được sử dụng cho logic Altera Debug Mater Endpoint (ADME) được Bộ công cụ thu phát sử dụng để có được quyền truy cập vào không gian CSR của bộ thu phát. Nó sẽ tự động bị hạn chế thay mặt bạn miễn là bạn có ít nhất một đồng hồ được tuyên bố khác trong thiết kế của mình thông qua lệnh SDC 'create_clock'. Để xác minh JTAG đã tự động bị hạn chế, hãy xem qua đầu ra của quartus_fit cho thông báo này:

"Thêm hạn chế thời gian mặc định vào tín hiệu JTAG. Điều này sẽ giúp đạt được chức năng cơ bản vì không có hạn chế như vậy do người dùng cung cấp."

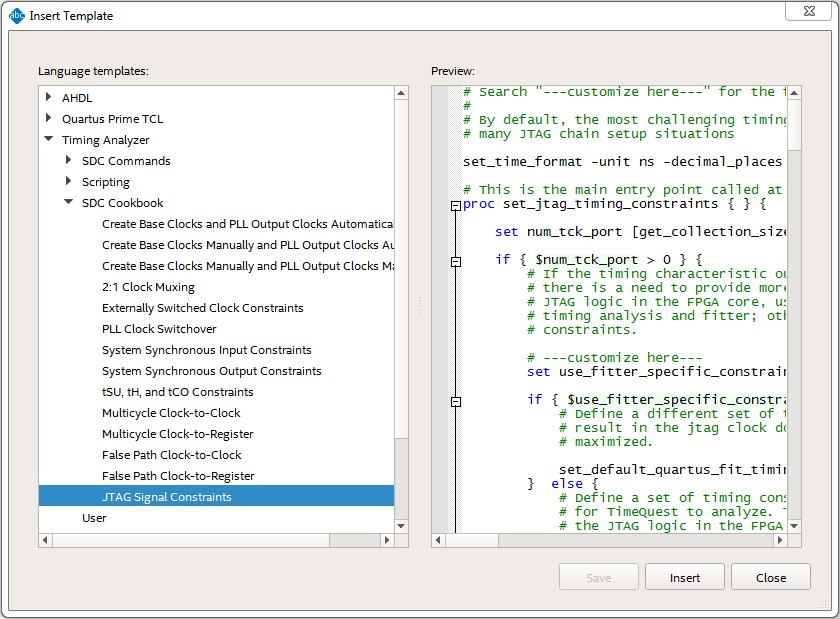

Ngoài ra, bạn có thể muốn chính xác hơn và hạn chế theo cách thủ công đồng hồ JTAG. Để làm điều này, hãy sử dụng mẫu thời gian SDC do Quartus cung cấp.

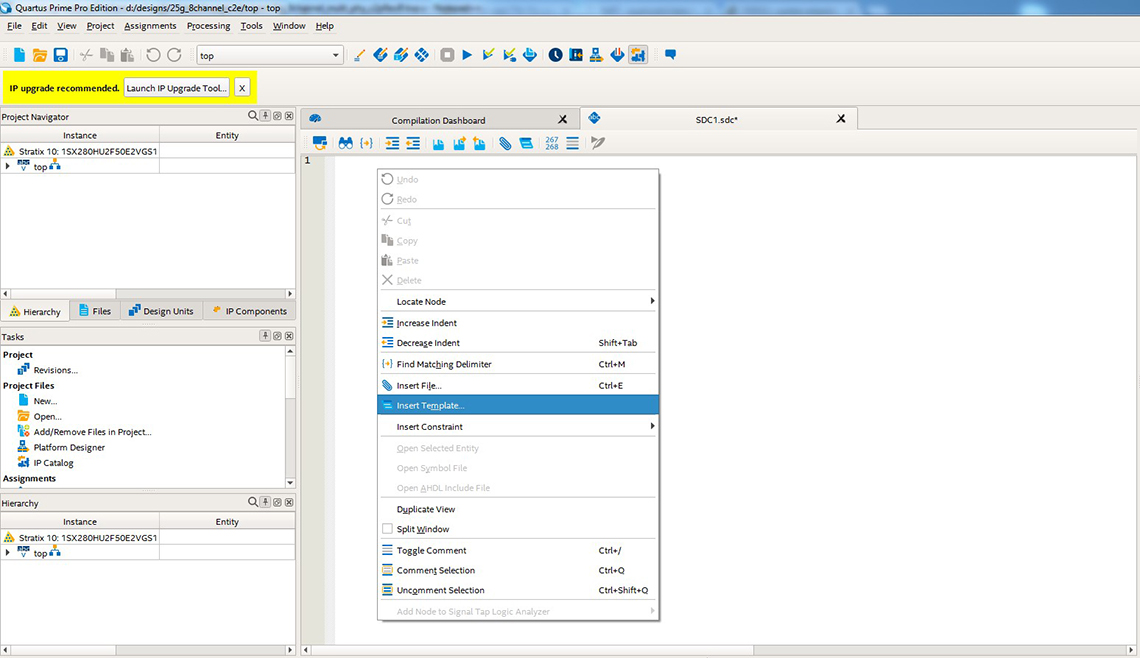

(1). Mở tệp SDC với Phiên bản Quartus Prime Pro ( Tệp -> Mở )

(2). Nhấp chuột phải vào cửa sổ tệp SDC để bật lên menu

(3). Chọn 'Chèn văn bản'

(4). Chọn 'Hạn chế tín hiệu JTAG' để chèn các hạn chế vào tệp SDC.